2. 프로세서 파이프라이닝 - 2025/08

파이프라이닝

CPU의 명령어 처리 과정을 크게 다음과 같이 나눕니다.

| IF (Instruction Fetch) | 메모리에서 명령어 읽어오기 |

| ID (Instruction Decode) | 명령어 해석, 필요한 레지스터/오퍼랜드 확인 |

| EX (Execute) | ALU나 FPU 등 실행 유닛에서 연산 수행 |

| MEM (Memory Access) | 필요한 경우 메모리 읽기/쓰기 |

| WB (Write Back) | 결과를 레지스터에 기록 |

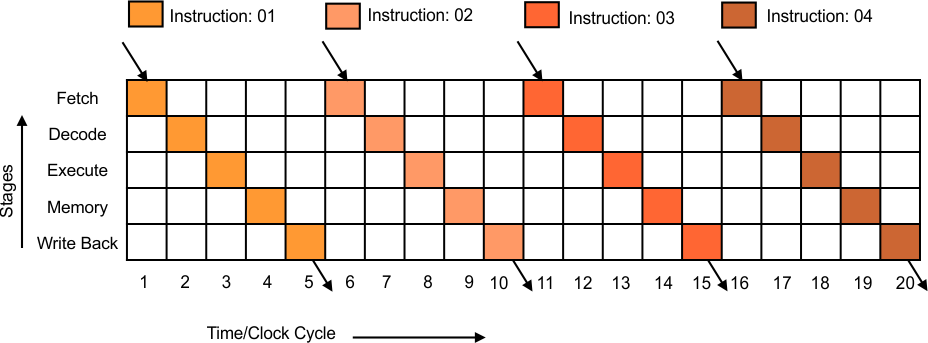

파이프라이닝을 사용하지 않는, 즉 순차처리를 진행한다면 다음과 같을 것 입니다.

하나의 명령어가 끝날때 까지 다음 명령어에 대한 처리가 일어나지 않습니다.

초기의 CPU가 이런 방식을 사용했습니다.

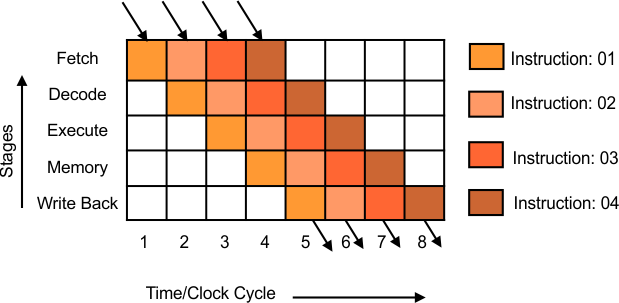

세분화 시킨 각 단계를 계속해서 수행할 수 있도록 CPU 내부를 모듈화 시켰고,

여러 명령어를 서로 다른 단계에서 동시에 처리가 가능하게 만듭니다.

이걸 파이프라이닝이라고 부릅니다.

파이프라인 해저드

이상적으로 N개로 나눈 파이프라인은 처리율이 N배로 높아질 수 있지만,

프로세서에서 파이프라인을 적용했을때는 이것이 쉽지 않습니다.

필연적으로 성능상에서 손해를 보는 상황이 나올 수 있는데,

이런 상황을 파이프라인 해저드라고 부릅니다.

구조 해저드(structural hazard)

구조 해저드는 프로세서의 자원이 부족해서 발생하는 스톨입니다.

두개의 명령어가 동시에 같은 자원을 원하는 상황이라면, 당연히 더 늦은 실행순서를 가지는

명령어 / 단계가 기다려야 합니다.

이를 해결하기 위해서는 최대한 많은 스테이지에 자원을 제공 할 수 있어야 합니다.

파이프라인이 N개인 프로세서라면, 한 사이클에 최대로 실행중인 스테이지는 N개일 것이고,

한 사이클에 하나의 장치에 접근하는 최대의 명령어 개수는 N개가 될 수 있을 것 입니다.

장치가 N개의 명령을 모두 커버할 수 있으면 그 어떠한 상황에서도 스톨을 피할 수 있을 것입니다.

예를 들면, 오퍼랜드를 로드 하는 작업과, 연산의 결과를 Write-back 하는 작업은 모두 레지스터에 접근합니다.

이를 해결 하기 위해서 레지스터 컴포넌트를 여러개 두는 방법을 사용합니다.

컨트롤 해저드(Control Hazard)

컨트롤 해저드는 프로그램이 가지는 근본적인 의존성으로 인해 발생합니다.

대표적인 예가 바로 조건 분기문 입니다.

프로그램에서 조건문이 없는 것은 상상하기 어렵습니다.

조건문은 조건식에 대한 평가, 즉 계산이 먼저 이루어져야만 점프하기 위한 위치를 알 수 있고,

그래야 PC를 구할 수 있습니다.

이를 해결 하기 위해서는 분기 예측을 고려 해 볼 수 있습니다.

FETCH 단계 에서 이것이 분기문이라면, 예측에 기반해서 명령을 인출하면 됩니다.

예측이 맞아 떨어지면 큰 성능 향상을 기대해 볼 수 있습니다.

만약 틀리다면, 파이프라인을 비워야 합니다.

데이터 해저드(Data Hazard)

데이터 해저드는 RAW/WAW/WAR 데이터 의존성과 메모리 의존성으로 발생합니다.

A = B + 1;

C = A + 2;

위 코드를 보면, A의 결과를 알아야 C를 계산할 수 있습니다.

RAW(Read After Write) 의 단순한 예 입니다.

A = B + 1; 의 A값이 Write-back 될 때까지 기다리는 데에서 오는 손해가 커질 수 있습니다.

결국 스톨로 이어질 수 있는 상황인데, 이럴 때에 스톨을 피하기 위해서

계산의 결과를 다시 ALU의 입력으로 피드백 시키는 방식을 사용합니다.

이런 방식을 포워딩이라고 합니다.

다음 명령어가 EX에서 즉시 사용 할 수 있도록 하는 것입니다.

또 다른 예시로 로드-유즈 해저드(Load-Use Hazard) 가 있습니다.

이 또한 대표적인 RAW의 케이스 중 하나입니다.

데이터를 로드하고, 그 로드 된 데이터를 사용하는 상황에서 발생합니다.

이 경우에는 EX에서 결과가 나오는게 아니고, MEM에서 로드된 데이터가 나오고 그걸

다음 명령어가 입력으로 받아야하는 상황입니다.

이러한 경우에는 당연히 스톨이 하나 발생 할 수 밖에 없는데,

현대 고성능 하드웨어에서는 설계상으로 이런 점을 회피 한다고 합니다.

'컴퓨터시스템' 카테고리의 다른 글

| 6. 가상 주소 변환 / TLB (0) | 2025.09.01 |

|---|---|

| 5. 분기 예측 (0) | 2025.09.01 |

| 4. 캐시 메모리 (0) | 2025.08.19 |

| 3. 비순차 실행, 슈퍼스칼라 (0) | 2025.08.15 |

| 1. 프로세서 인터페이스 ISA (0) | 2025.07.19 |